# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(11) 공개번호 10-2018-0079699(43) 공개일자 2018년07월11일

(51) 국제특허분류(Int. Cl.) *G09G 3/32* (2016.01)

(52) CPC특허분류 *G09G 3/32* (2013.01)

G09G 2310/027 (2013.01)

(21) 출원번호 **10-2017-0000203**

(22) 출원일자 **2017년01월02일** 심사청구일자 **2017년01월02일**  (71) 출원인

(주)실리콘인사이드

서울특별시 서초구 논현로 163, 302호(양재동, 인 환빌딩)

(72) 발명자

김진혁

서울특별시 강남구 선릉로 221, 203동 301호

김종선

경기도 화성시 동탄대로22길 30 센트럴자이

606-801 (74) 대리인

김경수

전체 청구항 수 : 총 7 항

(54) 발명의 명칭 드라이빙 PMOS 임계전압의 영향을 감소시킨 μLED 픽셀 구조 제어 방법

## (57) 요 약

본 발명은  $\mu$ LED 픽셀 구조를 제어하는 방법에 관한 것으로서, 보다 상세하게는  $\mu$ LED로 흐르는 전류의 크기를 결정하는데 있어 드라이빙 PMOS 임계전압의 영향을 감소시키거나 또는 제거함으로써  $\mu$ LED의 그레이스케일을 보다 용이하게 제어할 수 있도록 하는  $\mu$ LED 픽셀 구조 제어 방법에 관한 것이다.

(뒷면에 계속)

대 표 도 - 도1

보다 구체적으로 본 발명에 대하여 설명하면, 본 발명은 프리차지 NMOS를 온(on) 시킴으로써, 드라이빙 PMOS의 게이트 바이어스(Gate Bias)를 0V 로 유지시키는 프리차지(Pre-Charge) 단계; 소스 드라이버(Source Driver)에서 μLED 픽셀에 데이터를 제공할 때, 상기 프리차지 NMOS와 인에이블 오프 PMOS를 오프(off) 시키고 인에이블 온 PMOS를 온 시킴으로써, 상기 드라이빙 PMOS의 게이트 바이어스가 (데이터값 - 드라이빙 PMOS의 임계전압) 이되도록 하는 데이터 인에이블(Data Enable) 단계; 및 상기 인에이블 오프 PMOS를 온 시키고 상기 인에이블 온 PMOS를 오프 시킴과 동시에, 오프 상태로 있던 에미션 NMOS와 에미션 PMOS를 온 시킴으로써, 드라이빙 PMOS의 게이트-소스전압에 따라 μLED로 전류가 흐르도록 하는 에미션(Emission) 단계; 를 포함하는 드라이빙 PMOS 임계전압의 영향을 감소시킨 μLED 픽셀 구조 제어 방법을 제공한다.

### 명세서

### 청구범위

#### 청구항 1

프리차지 NMOS를 온(on) 시킴으로써, 드라이빙 PMOS의 게이트 바이어스(Gate Bias)를 0V 로 유지시키는 프리차지(Pre-Charge) 단계;

소스 드라이버(Source Driver)에서  $\mu$  LED 픽셀에 데이터를 제공할 때, 상기 프리차지 NMOS와 인에이블 오프 PMOS를 오프(off) 시키고 인에이블 온 PMOS를 온 시킴으로써, 상기 드라이빙 PMOS의 게이트 바이어스가 (데이터 값 - 드라이빙 PMOS의 임계전압) 이 되도록 하는 데이터 인에이블(Data Enable) 단계; 및

상기 인에이블 오프 PMOS를 온 시키고 상기 인에이블 온 PMOS를 오프 시킴과 동시에, 오프 상태로 있던 에미션 NMOS와 에미션 PMOS를 온 시킴으로써, 드라이빙 PMOS의 게이트-소스전압에 따라  $\mu$ LED로 전류가 흐르도록 하는 에미션(Emission) 단계; 를 포함하는 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조 제어 방법.

## 청구항 2

제 1항에 있어서,

상기 인에이블 온 PMOS와 인에이블 오프 PMOS는 컨버터(Converter)를 이용해 각각의 게이트에 반대되는 전압을 제공함으로써 서로 반대의 온 또는 오프 동작을 하도록 제어하는 것을 특징으로 하는 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조 제어 방법.

### 청구항 3

제 1항에 있어서,

상기 에미션 NMOS와 에미션 PMOS는 컨버터를 이용해 각각의 게이트에 반대되는 전압을 제공함으로써 서로 동일 한 온 또는 오프 동작을 하도록 제어하는 것을 특징으로 하는 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$  LED 픽셀 구조 제어 방법.

## 청구항 4

제 1항에 있어서,

상기 인에이블 온 PMOS는 제1 인에이블 온 PMOS 및 제2 인에이블 온 PMOS를 포함하며,

상기 제1 인에이블 온 PMOS는 드레인이 상기 드라이빙 PMOS의 소스에 연결되도록 배치되고,

상기 제2 인에이블 온 PMOS는 소스가 상기 드라이빙 PMOS의 드레인에, 드레인이 상기 드라이빙 PMOS의 게이트에 연결되도록 배치되는 것을 특징으로 하는 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조 제어 방법.

### 청구항 5

제 1항에 있어서,

상기 전류는 다음의 수식으로 결정되며,

$I_D = (\mu_n C_{ox}/2)(W/L)(V_{GS} - V_{TH})^2$

$I_D$ 는 전류,  $\mu_n$ 은 전자 mobility,  $C_{ox}$ 는 드라이빙 PMOS 게이트의 커패시턴스(Capacitance), W는 드라이빙 PMOS 게이트의 폭, L은 드라이빙 PMOS 게이트의 길이,  $V_{GS}$ 는 드라이빙 PMOS의 게이트-소스전압,  $V_{TH}$ 는 드라이빙 PMOS의 임계전압에 해당하는 것을 특징으로 하는 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조 제어방법.

#### 청구항 6

제 5항에 있어서.

상기 드라이빙 PMOS의 게이트-소스전압( $V_{GS}$ )은 (전원전압 - 데이터값 + 드라이빙 PMOS의 임계전압) 이 되는 것을 특징으로 하는 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조 제어 방법.

#### 청구항 7

제 1항에 있어서,

상기 uLED 픽셀은 다수로 매트릭스를 이룸으로써 디스플레이를 구성하며,

상기 디스플레이는,

매트릭스를 이룬 μLED 픽셀들의 행을 스캔하는 스캔 컨트롤러(Scan Controller);

상기 스캔 컨트롤러가 스캔하는 행의 해당 µLED 픽셀들에 데이터를 제공하는 소스 드라이버;

상기 스캔 컨트롤러와 소스 드라이버의 타이밍을 제어하는 타이밍 컨트롤러(Timing Controller); 및

직렬 주변 장치 인터페이스(Serial Peripheral Interface: SPI), 저전압 차등 시그널링(Low Voltage Differential Signaling) 또는 RGB(Red-Green-Blue) 인터페이스 중 어느 하나 이상을 포함하는 인터페이스; 를 포함하는 DDI(Display Driver IC)에 의해 제어되는 것을 특징으로 하는 드라이빙 PMOS 임계전압의 영향을 감소시킨 μLED 픽셀 구조 제어 방법.

#### 발명의 설명

## 기술분야

[0001] 본 발명은 μLED 픽셀 구조를 제어하는 방법에 관한 것으로서, 보다 상세하게는 μLED로 흐르는 전류의 크기를 결정하는데 있어 드라이빙 PMOS 임계전압의 영향을 감소시키거나 또는 제거함으로써 μLED의 그레이스케일을 보다 용이하게 제어할 수 있도록 하는 μLED 픽셀 구조 제어 방법에 관한 것이다.

### 배경기술

- [0003] 최근 LCD(Liquid Crystal Display)와 OLED(Organic Light Emitting Diode) 이후 차세대 디스플레이로 μ LED(Micro-LED)가 주목받고 있다.

- [0004] µLED는 통상적으로 칩 크기가 5 ~ 10µm에 불과한 초소형 LED를 말하는데, LED 칩 자체를 화소로 활용할 수 있 기 때문에 기존 LED로 구현할 수 없는 휘어짐이나 깨짐 등의 문제를 극복할 수 있는 특징이 있다.

- [0005] 초소형 입자를 발광재료로 사용한다는 점에서는 퀀텀닷(Quantum Dot)과 비슷하지만, 저전력, 소형화, 경량화 측면에서는 더욱 개선된 성능을 보인다는 것이 장점이다.

- [0006] 플렉서블 디스플레이(Flexible Display), 섬유와 LED가 결합한 스마트 섬유, 인체 부착 및 삽입형 의료기기, 바이오 콘택트렌즈, 가상현실(VR) 디스플레이 등 다양한 산업군과 융복합이 가능해지는 확장성 측면에서도 각광받고 있는 실정이다.

- [0007] 디스플레이를 구현하기 위하여 이러한 µLED는 픽셀 단위로 구성되어 웨이퍼 상에 매트릭스를 이루도록 다수로

장착되는데, 각각의  $\mu$ LED 픽셀 구조에는 드라이빙 PMOS(Driving P-channel Metal Oxide Semiconductor)가  $\mu$ LED로 흐르는 전류를 제어함으로써  $\mu$ LED의 그레이스케일을 조절하게 된다.

- [0008] 상기 전류는 전자 mobility, 드라이빙 PMOS의 특정 수치나 소자 특성 등 다양한 파라미터들에 의해 결정되는데, 대부분은 공정 과정에서 제어가 가능하지만 드라이빙 PMOS의 임계전압은 그렇지 못한 문제점이 있다.

- [0009] 왜냐하면 아무런 조치를 취하지 않는 경우 상기 드라이빙 PMOS의 임계전압에 의해 μLED의 그레이스케일은 ± 15%의 산포(散布)를 보이게 되며, 이는 μLED를 이용한 디스플레이의 개발과 상용화에 큰 문제가 아닐 수 없기 때문이다.

- [0010] 따라서, µLED로 흐르는 전류를 결정하는데 있어 드라이빙 PMOS 임계전압의 영향을 제거하거나 감소시킬 수 있는 구조 또는 방법이 매우 필요하다.

## 발명의 내용

## 해결하려는 과제

- [0012] 본 발명은 전술한 종래기술의 문제점을 해결하기 위해 안출된 것으로서, μLED 픽셀 구조에서 드라이빙 PMOS 임계전압의 영향을 제거 또는 감소시킴으로써 μLED의 그레이스케일을 보다 용이하게 제어할 수 있도록 하는 μLED 픽셀 구조 제어 방법을 제공하는데 그 목적이 있다.

- [0013] 본 발명이 이루고자 하는 기술적 과제들은 이상에서 언급한 기술적 과제들로 제한되지 않으며, 언급되지 않은 또 다른 기술적 과제들은 본 발명의 기재로부터 당해 분야에서 통상의 지식을 가진 자에게 명확하게 이해될 수 있을 것이다.

#### 과제의 해결 수단

- [0015] 상술한 종래기술의 문제점을 해결하기 위한 본 발명에 의하면, 프리차지 NMOS를 온(on) 시킴으로써, 드라이빙 PMOS의 게이트 바이어스(Gate Bias)를 0V 로 유지시키는 프리차지(Pre-Charge) 단계; 소스 드라이버(Source Driver)에서 μLED 픽셀에 데이터를 제공할 때, 상기 프리차지 NMOS와 인에이블 오프 PMOS를 오프(off) 시키고 인에이블 온 PMOS를 온 시킴으로써, 상기 드라이빙 PMOS의 게이트 바이어스가 (데이터값 드라이빙 PMOS의 임 계전압) 이 되도록 하는 데이터 인에이블(Data Enable) 단계; 및 상기 인에이블 오프 PMOS를 온 시키고 상기 인에이블 온 PMOS를 오프 시킴과 동시에, 오프 상태로 있던 에미션 NMOS와 에미션 PMOS를 온 시킴으로써, 드라이빙 PMOS의 게이트-소스전압에 따라 μLED로 전류가 흐르도록 하는 에미션(Emission) 단계; 를 포함하는 드라이빙 PMOS 임계전압의 영향을 감소시킨 μLED 픽셀 구조 제어 방법을 제공한다.

- [0016] 본 발명에서 상기 인에이블 온 PMOS와 인에이블 오프 PMOS는 컨버터(Converter)를 이용해 각각의 게이트에 반대되는 전압을 제공함으로써 서로 반대의 온 또는 오프 동작을 하도록 제어하는 것이 바람직하다.

- [0017] 본 발명에서 상기 에미션 NMOS와 에미션 PMOS는 컨버터를 이용해 각각의 게이트에 반대되는 전압을 제공함으로 써 서로 동일한 온 또는 오프 동작을 하도록 제어하는 것이 바람직하다.

- [0018] 본 발명에서 상기 인에이블 온 PMOS는 제1 인에이블 온 PMOS 및 제2 인에이블 온 PMOS를 포함하며, 상기 제1 인에이블 온 PMOS는 드레인이 상기 드라이빙 PMOS의 소스에 연결되도록 배치되고, 상기 제2 인에이블 온 PMOS는 소스가 상기 드라이빙 PMOS의 드레인에, 드레인이 상기 드라이빙 PMOS의 게이트에 연결되도록 배치되는 것이 바람직하다.

- [0019] 본 발명의 상기 전류는 다음의 수식으로 결정되며,

- $I_D = (\mu_n C_{ox}/2)(W/L)(V_{GS} V_{TH})^2$

- [0021]  $I_D$ 는 전류,  $\mu_n$ 은 전자 mobility,  $C_{ox}$ 는 드라이빙 PMOS 게이트의 커패시턴스(Capacitance), W는 드라이빙 PMOS 게이트의 폭, L은 드라이빙 PMOS 게이트의 길이,  $V_{GS}$ 는 드라이빙 PMOS의 게이트-소스전압,  $V_{TH}$ 는 드라이빙 PMOS의 의 임계전압에 해당하도록 구성된다.

- [0022] 본 발명에서 상기 드라이빙 PMOS의 게이트-소스전압(V<sub>GS</sub>)은 (전원전압 데이터값 + 드라이빙 PMOS의 임계전압) 이 되도록 구성된다.

- [0023] 본 발명에서 상기 μLED 픽셀은 다수로 매트릭스를 이룸으로써 디스플레이를 구성하며, 상기 디스플레이는, 매트릭스를 이룬 μLED 픽셀들의 행을 스캔하는 스캔 컨트롤러(Scan Controller); 상기 스캔 컨트롤러가 스캔하는 행의 해당 μLED 픽셀들에 데이터를 제공하는 소스 드라이버; 상기 스캔 컨트롤러와 소스 드라이버의 타이밍을 제어하는 타이밍 컨트롤러(Timing Controller); 및 직렬 주변 장치 인터페이스(Serial Peripheral Interface: SPI), 저전압 차등 시그널링(Low Voltage Differential Signaling) 또는 RGB(Red-Green-Blue) 인터페이스 중 어느 하나 이상을 포함하는 인터페이스; 를 포함하는 DDI(Display Driver IC)에 의해 제어되는 것이 바람직하다.

#### 발명의 효과

- [0025] 본 발명은 μLED 픽셀 구조에 있어서 NMOS와 PMOS 등의 소자 특성을 이용해 μLED로 흐르는 전류에 드라이빙 PMOS 임계전압의 영향을 제거하거나 감소시키는 효과가 있다.

- [0026] 이에 따라, 본 발명은  $\mu$ LED의 그레이스케일을 보다 용이하게 제어할 수 있으며, 종래  $\mu$ LED의 그레이스케일이 가지던  $\pm 15\%$ 의 산포를 보다 감소시켜  $\pm 1.5\%$  이내의 산포를 갖도록 하는 효과가 있다.

- [0027] 결과적으로 본 발명은 µLED를 이용한 디스플레이의 효율과 성능을 향상시켜 보다 저전력으로 소형화/경량화 가능한 디스플레이 장치들을 개발 및 상용화할 수 있도록 하는 효과가 있다.

## 도면의 간단한 설명

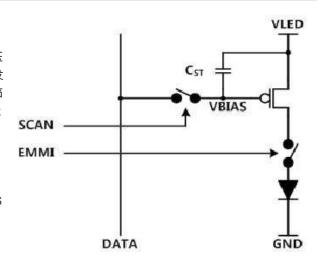

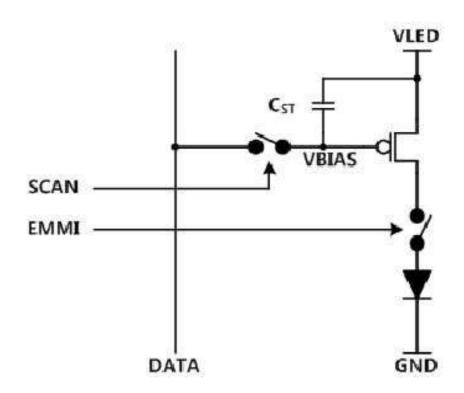

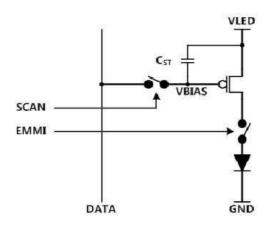

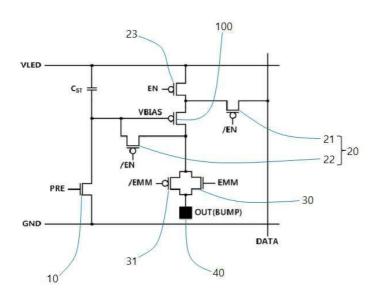

[0029] 도 1은 본 발명의 일실시예에 따른 μLED 픽셀 구조 제어 방법의 기본적인 개념을 나타낸 예시도.

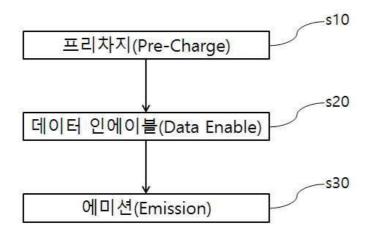

도 2는 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$  LED 픽셀 구조 제어 방법 순서 도.

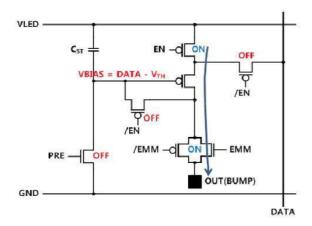

도 3은 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조를 나타낸 예시도.

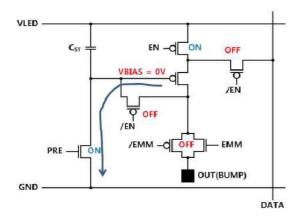

도 4a는 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조 제어 방법의 프리차지 단계를 나타낸 예시도.

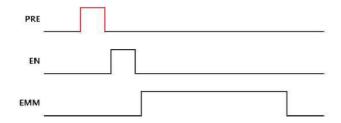

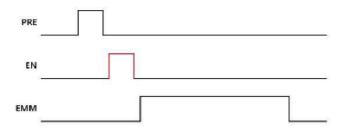

도 4b는 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조 제어 방법의 프리차지 단계 시 인가 신호를 나타낸 예시도.

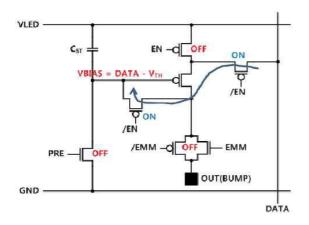

도 5a는 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨 μLED 픽셀 구조 제어 방법의 데이터 인에이블 단계를 나타낸 예시도.

도 5b는 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조 제어 방법의 데이터 인에이블 단계 시 인가 신호를 나타낸 예시도.

도 6a는 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨 μLED 픽셀 구조 제어 방법의에미션 단계를 나타낸 예시도.

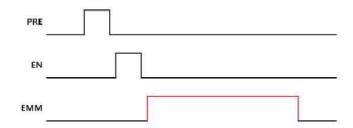

도 6b는 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조 제어 방법의에미션 단계 시 인가 신호를 나타낸 예시도.

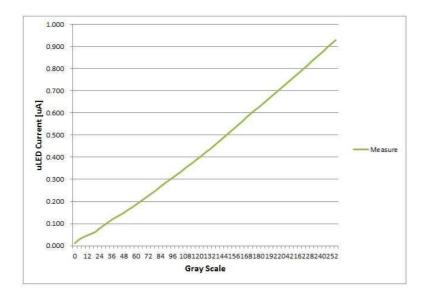

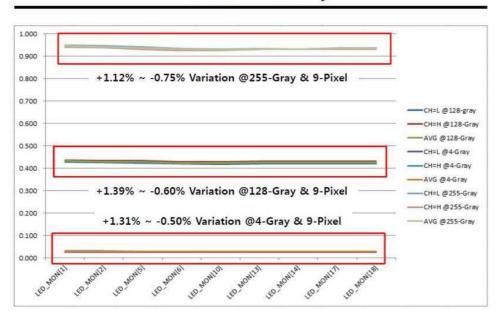

도 7은 본 발명의 일실시예에 따른 μLED 그레이스케일에 대한 μLED 전류를 측정한 결과를 나타낸 예시도.

도 8은 본 발명의 일실시예에 따른 세 가지 그레이값에 대한 픽셀 데이터를 측정한 결과를 나타낸 예시도.

## 발명을 실시하기 위한 구체적인 내용

[0030] 이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 상세히 설명하기로 한다. 이에 앞서, 본 명세서 및

특허청구범위에 사용된 용어나 단어는 통상적이거나 사전적인 의미로 한정하여 해석되어서는 안되며, 발명자는 그 자신의 발명을 가장 최선의 방법으로 설명하기 위해 용어의 개념을 적절하게 정의할 수 있다는 원칙에 입각하여 본 발명의 기술적 사상에 부합하는 의미와 개념으로 해석되어야만 한다. 따라서, 본 명세서에 기재된 실시예와 도면에 도시된 구성은 본 발명의 가장 바람직한 일실시예에 불과할 뿐 본 발명의 기술적 사상을 모두 대변하는 것은 아니므로, 본 출원시점에 있어서 이들을 대체할 수 있는 다양한 균등물과 변형예들이 있을 수 있음을 이해하여야 한다.

- [0031] 본 명세서에서 사용된 용어는 특정 실시예를 설명하기 위하여 사용되므로 본 발명을 제한하기 위한 것이 아니다. 본 명세서에서 사용된 바와 같이, 단수 형태는 문맥상 다른 경우를 분명히 지적하는 것이 아니라면 복수의 형태를 포함할 수 있다.

- [0033] 먼저, 도 1에는 본 발명의 일실시예에 따른 µLED 픽셀 구조 제어 방법의 기본적인 개념을 나타낸 예시도가 도 시된다.

- [0034] μLED 픽셀들이 다수로 매트릭스를 형성함으로써 디스플레이를 구성하는 가운데, 본 도면은 하나의 μLED 픽셀 구조의 개념을 나타낸 것으로, μLED 픽셀들의 행을 스캔하는 스캔 컨트롤러에 의한 스캔 데이터와, 해당 μLED 픽셀들에 데이터를 제공하는 소스 드라이버에 의한 소스 데이터가 타이밍 컨트롤러의 타이밍 제어에 의해 μLED 픽셀에 제공된다.

- [0035] 이 때 드라이빙 PMOS(Driving P-channel Metal Oxide Semiconductor)(100)의 게이트-소스전압에 의해 μ LED(40)로 흐르는 전류가 결정되는데, 상기 전류의 크기는 다음과 같다.

- [0036]  $I_D = (\mu_n C_{ox}/2)(W/L)(V_{GS} V_{TH})^2$

- [0037] 여기서  $I_D$ 는 전류,  $\mu_n$ 은 전자 mobility,  $C_{ox}$ 는 드라이빙 PMOS 게이트의 커패시턴스(Capacitance), W는 드라이빙 PMOS 게이트의 폭, L은 드라이빙 PMOS 게이트의 길이,  $V_{GS}$ 는 드라이빙 PMOS의 게이트-소스전압,  $V_{TH}$ 는 드라이빙 PMOS의 임계전압에 해당한다.

- [0038] 위의 수식으로 표현될 수 있는 μLED(40)로 흐르는 전류의 크기는, 해당 μLED의 그레이스케일(Grayscale)을 결정하는데, 상기 전류는 다양한 파라미터들에 의해 결정되고 대부분은 공정 과정에서 쉽게 제어가 가능하지만, 드라이빙 PMOS(100)의 임계전압(Threshold Voltage)은 현재의 공정 기술로는 제어하기가 어려워 별다른 조치를 취하지 않을 경우 μLED의 그레이스케일은 ±15% 정도의 산포를 보이게 된다.

- [0039] 따라서 μLED(40)로 흐르는 전류에서 드라이빙 PMOS(100) 임계전압의 영향을 제거하거나 또는 감소시킴으로써 μLED 그레이스케일의 산포를 낮추고 이를 용이하게 제어할 수 있도록 하는 본 발명은, 프리차지 NMOS(Pre-Charge N-channel Metal Oxide Semiconductor)(10)를 온(on) 시킴으로써, 드라이빙 PMOS의 게이트 바이어스 (Gate Bias)를 0V 로 유지시키는 프리차지(Pre-Charge) 단계, 소스 드라이버(Source Driver)에서 μLED 픽셀에 데이터를 제공할 때, 상기 프리차지 NMOS와 인에이블 오프 PMOS(23)를 오프(off) 시키고 인에이블 온 PMOS(20)를 온 시킴으로써, 상기 드라이빙 PMOS의 게이트 바이어스가 (데이터값 드라이빙 PMOS의 임계전압) 이 되도록 하는 데이터 인에이블(Data Enable) 단계 및 상기 인에이블 오프 PMOS를 온 시키고 상기 인에이블 온 PMOS를 오프 시킴과 동시에, 오프 상태로 있던 에미션 NMOS(30)와 에미션 PMOS(31)를 온 시킴으로써, 드라이빙 PMOS의 게이트-소스전압에 따라 μLED로 전류가 흐르도록 하는 에미션(Emission) 단계를 포함하여 구성된다.

- [0041] 이에 대한 이해를 돕기 위해, 도 2에는 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조 제어 방법 순서도가 도시되고, 도 3에는 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨  $\mu$ LED 픽셀 구조를 나타낸 예시도가 도시되며, 도면을 참조하여 본 발명을 구성하는 각각의 단계들을 설명하면 다음과 같다.

- [0043] 먼저 본 발명은 도 4b에 도시된 것과 같이 프리(PRE) 신호에 따라 프리차지 NMOS(10)를 온 시켜 드라이빙 PMOS(100)의 게이트 바이어스를 0V 가 되도록 하고, 이를 유지시키는 프리차지 단계가 수행된다(s10).

- [0044] 도 4a에 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨 µLED 픽셀 구조 제어 방법의

프리차지 단계를 나타낸 예시도가 도시되는데, 이 때에는 다른 PMOS나 NMOS(인에이블 온 PMOS(20), 에미션 NMOS(30), 에미션 PMOS(31))는 모두 오프 상태에 놓이며, 인에이블 오프 PMOS(23)만 온 상태에 있는 것이 바람 직하다. μLED(40) 방향으로 원치 않는 전류가 무단으로 흐르는 것을 방지하기 위함이다.

- [0045] 따라서, 본 단계에서는 프리차지 NMOS(10)가 온 상태에 놓여 드라이빙 PMOS(100)의 게이트에서 상기 프리차지 NMOS 방향으로 전류가 흐르게 됨으로써 상기 드라이빙 PMOS의 게이트 바이어스가 0V 로 유지된다.

- [0047] 이후, 소스 드라이버에서 µLED 픽셀에 데이터를 제공할 때 상기 드라이빙 PMOS(100)의 게이트 바이어스가 (데이터값 드라이빙 PMOS의 임계전압) 이 되도록 하는 데이터 인에이블 단계가 진행된다(s20).

- [0048] 본 단계는 프라차지 단계 이후, µLED 픽셀을 초기화하여 데이터 입력을 받을 준비를 완료하는 단계로서, 도 5b에 도시된 것과 같은 인에이블(EN) 신호에 따라 상기 프리차지 단계에서 온 상태에 놓여있던 프리차지 NMOS(10)와 인에이블 오프 PMOS(23)를 오프 상태에 놓이도록 하고, 이와 동시에 인에이블 온 PMOS(20)를 온 상태에 놓음으로써 드라이빙 PMOS(100)의 게이트 바이어스가 (데이터값 드라이빙 PMOS의 임계전압) 이 되도록 한다.

- [0049] 도 5a에는 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨 µLED 픽셀 구조 제어 방법의 데이터 인에이블 단계를 나타낸 예시도가 도시된다.

- [0050] 도면을 참조하여 보다 상세히 설명하면, 상기 인에이블 온 PMOS(20)는 제1 인에이블 온 PMOS(21) 및 제2 인에이블 온 PMOS(22)를 포함하고, 상기 제1 인에이블 온 PMOS는 드레인이 드라이빙 PMOS(100)의 소스에 연결되도록 배치됨과 동시에 상기 제2 인에이블 온 PMOS는 소스가 상기 드라이빙 PMOS의 드레인에, 드레인이 상기 드라이빙 PMOS의 게이트에 연결되도록 배치되어 제1 인에이블 온 PMOS에서 제2 인에이블 온 PMOS로 전류가 흐르고, 결과 적으로 드라이빙 PMOS의 게이트에는 소스 드라이버에서 입력한 데이터값에서 드라이빙 PMOS의 임계전압을 뺀 값 (데이터값 드라이빙 PMOS의 임계전압)만큼의 전압이 충전된다.

- [0051] 여기에서 상기 인에이블 온 PMOS(20)와 인에이블 오프 PMOS(23)에는 각각의 게이트에 컨버터(Converter)를 이용하여 서로 반대되는 전압을 제공함으로써 온 또는 오프 동작을 서로 반대로 수행하도록 하는 것이 바람직하다.

- [0053] 그리고 마지막으로 드라이빙 PMOS(100)에 충전된 게이트-소스전압에 따라 µLED(40)로 전류가 흐르는 에미션 단계가 수행된다(s30).

- [0054] 본 단계는 도 6b에 도시된 것처럼 에미션(EMM) 신호에 따라 상기 인에이블 오프 PMOS(23)를 온 시키고 상기 인에이블 온 PMOS(20)를 오프 시킴과 동시에, 오프 상태로 있던 에미션 NMOS(30)와 에미션 PMOS(31)를 온 시킴으로써 이루어지며, 이 때 흐르는 전류는 ID = (μηCox/2)(W/L)(V<sub>GS</sub> V<sub>TH</sub>)<sup>2</sup> 으로 결정된다.

- [0055] 도 6a에 본 발명의 일실시예에 따른 드라이빙 PMOS 임계전압의 영향을 감소시킨 μLED 픽셀 구조 제어 방법의 에미션 단계를 나타낸 예시도가 도시되며, 이 단계에서는 상기 드라이빙 PMOS(100)의 게이트-소스전압(V<sub>GS</sub>)이 (전원전압 데이터값 + 드라이빙 PMOS의 임계전압) 이 되므로, 상기 전류에서 드라이빙 PMOS의 임계전압은 사라져 아무런 영향을 미치지 않는다.

- [0056] 앞의 단계와 마찬가지로, 상기 에미션 NMOS(30)와 에미션 PMOS(31)에는 컨버터를 이용해 각각의 게이트에 반대되는 전압을 제공함으로써 서로 동일한 온 또는 오프 동작을 하도록 제어되는 것을 특징으로 한다.

- [0058] 위와 같은 단계들로 구성된 본 발명의 결과를 보이기 위해, 도 7에는 본 발명의 일실시예에 따른  $\mu$ LED 그레이스케일에 대한  $\mu$ LED 전류를 측정한 결과를 나타낸 예시도가 도시되고, 도 8에는 본 발명의 일실시예에 따른 세 가지 그레이값에 대한 픽셀 데이터를 측정한 결과를 나타낸 예시도가 도시된다.

- [0059] 먼저 도 7을 보면, μLED 그레이스케일(총 0 그레이(black)에서 255 그레이(white)로 256 그레이 단계)에 대한 μLED(40) 전류를 측정한 결과를 나타내며, 0 그레이에서 255 그레이까지 선형(linear)적인 곡선을 획득한 것을 알 수 있다.

- [0060] 그리고 도 8은 4 그레이(저), 128 그레이(중), 255 그레이(고) 세 가지 그레이값에 대한 9개의 픽셀 데이터를 수집한 것을 나타낸다.

- [0061] 본 측정 도면에서는 앞서 설명한 바와 같이, 그레이스케일이 ±1.5% 이내의 산포를 보이는 것을 확인할 수 있으며, 여기서 0 그레이가 아닌 4 그레이로 데이터 측정을 한 이유는, 0 그레이는 전류가 "0"에 가깝기 때문에 데이터로서 의미가 없으므로, 측정데이터로서의 요건을 만족하기 위해 임의의 4 그레이를 선택하여 측정하였다.

- [0063] 전체적으로 본 발명은 위와 같은 μLED 픽셀이 다수로 매트릭스를 이룸으로써 디스플레이를 구성하게 되는데, 상기 디스플레이는, 매트릭스를 이룬 μLED 픽셀들의 행을 스캔하는 스캔 컨트롤러(Scan Controller), 상기 스캔 컨트롤러가 스캔하는 행의 해당 μLED 픽셀들에 데이터를 제공하는 소스 드라이버, 상기 스캔 컨트롤러와 소스 드라이버의 타이밍을 제어하는 타이밍 컨트롤러(Timing Controller) 및 직렬 주변 장치 인터페이스(Serial Peripheral Interface: SPI), 저전압 차등 시그널링(Low Voltage Differential Signaling) 또는 RGB(Red-Green-Blue) 인터페이스 중 어느 하나 이상을 포함하는 인터페이스를 포함하는 DDI(Display Driver IC)에 의해 제어되는 것이 바람직하다.

- [0065] 결과적으로, 본 발명은 μLED 픽셀 구조에 있어서 NMOS와 PMOS 등의 소자 특성을 이용해 μLED로 흐르는 전류에 드라이빙 PMOS 임계전압의 영향을 제거하거나 감소시키는 장점이 있다.

- [0066] 이에 따라, 본 발명은  $\mu$ LED의 그레이스케일을 보다 용이하게 제어할 수 있으며, 종래  $\mu$ LED의 그레이스케일이 가지던  $\pm 15\%$ 의 산포를 보다 감소시켜  $\pm 1.5\%$  이내의 산포를 갖도록 한다.

- [0067] 즉, 본 발명은 µLED를 이용한 디스플레이의 효율과 성능을 향상시켜 보다 저전력으로 소형화/경량화 가능한 디스플레이 장치들을 개발 및 상용화할 수 있도록 하는 개선된 장점이 있다.

- [0069] 이상 본 발명의 구체적 실시형태와 관련하여 본 발명을 설명하였으나, 이는 예시에 불과하며 본 발명은 이에 제한되지 않는다. 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자는 본 발명의 범위를 벗어나지 않고 설명된 실시형태를 변경 또는 변형할 수 있으며, 본 발명의 기술사상과 아래에 기재될 특허청구범위의 균등범위 내에서 다양한 수정 및 변형이 가능하다.

## 부호의 설명

[0071] 10: 프리차지 NMOS

20: 인에이블 온 PMOS

21: 제1 인에이블 온 PMOS

22: 제2 인에이블 온 PMOS

23: 인에이블 오프 PMOS

30: 에미션 NMOS

31: 에미션 PMOS

40: μ LED

100: 드라이빙 PMOS

# 도면

# 도면1

# 도면2

# 도면3

# 도면4a

# *도면4b*

# 도면5a

# *도면5b*

# 도면6a

# 도면6b

# 도면7

## 도면8

## **LED Current Uniformity**

| 专利名称(译)        | MLED像素结构控制方法,具有降                           | K低驱动PMOS阈值电压的影响 |            |  |

|----------------|--------------------------------------------|-----------------|------------|--|

| 公开(公告)号        | KR1020180079699A                           | 公开(公告)日         | 2018-07-11 |  |

| 申请号            | KR1020170000203                            | 申请日             | 2017-01-02 |  |

| [标]申请(专利权)人(译) | SILICONINSIDE                              |                 |            |  |

| 申请(专利权)人(译)    | (株)硅内幕                                     |                 |            |  |

| 当前申请(专利权)人(译)  | (株)硅内幕                                     |                 |            |  |

| [标]发明人         | KIM JIN HYUK<br>김진혁<br>KIM JONG SUN<br>김종선 |                 |            |  |

| 发明人            | 김진혁<br>김종선                                 |                 |            |  |

| IPC分类号         | G09G3/32                                   |                 |            |  |

| CPC分类号         | G09G3/32 G09G2310/027                      |                 |            |  |

| 代理人(译)         | Gimgyeongsu                                |                 |            |  |

| 外部链接           | Espacenet                                  |                 |            |  |

|                |                                            |                 |            |  |

## 摘要(译)

本发明涉及μLED像素结构的控制方法,更具体地说,涉及μLED像素结构控制方法,用于确定流向μLED的电流大小,降低驱动PMOS临界电压的影响或更容易控制通过去除μLED的灰度级。更具体地,它说明了本发明。并且本发明提供了μLED像素结构控制方法,其减小了驱动PMOS临界电压的影响,该方法包括来自预充电NMOS的发光步骤,并且其产生;它提供预充电(预充电)步骤中的数据:源极驱动器,其将驱动PMOS的栅极偏压保持在0V至μLED像素;它使PMOS产生预充电NMOS,并在关闭(关闭)时关闭PMOS并启用启用;它关闭数据使能步骤:执行和PMOS关闭PMOS使能,并启用(on)使其成为驱动PMOS的栅极偏置(数据值的临界电压 - 驱动PMOS)一个;它将发射NMOS和发射PMOS变为OFF状态;并且电流根据驱动PMOS的栅极 - 源极电压流向μLED。